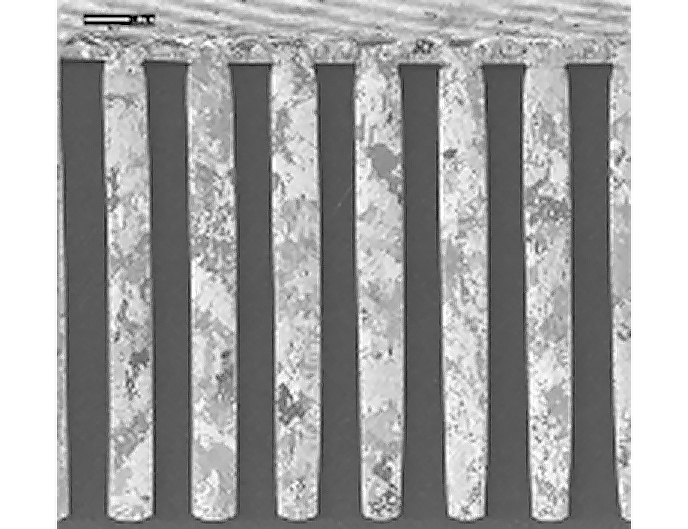

Through Silicon Via (TSV) interconnects are used in high performance, low power 2.5D and 3D package integration

TSV enables stacking for 3D memory and 2.5D heterogeneous integration for improved electrical performance driven by greater package complexity, higher integration levels and the need for shorter interconnections. TSV for 2.5D integrations allows multiple chips to be connected through a passive interposer that enables die-to-die communication. CMOS Image Sensors (CIS), Stacked Memory and WLCSP will continue to use TSV technology as higher performance packages evolve.